Blackfin

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Read other articles:

Akademi Komunitas Industri Manufaktur BantaengDidirikan2018Lembaga indukKementerian Perindustrian Republik IndonesiaDirekturDrs. Zainal Abidin, M.SiAlamatNipa-Nipa, Pa’jukukang, BantaengSitus webwww.akom-bantaeng.ac.id Akademi Komunitas Industri Manufaktur Bantaeng atau AK-Manufaktur Bantaeng adalah pendidikan tinggi Vokasi di bidang teknologi manufaktur yang berada di bawah Kementerian Perindustrian Republik Indonesia untuk memenuhi kebutuhan tenaga ahli manufaktur. Kampus ini terletak di Kab…

Fictional vigilantes in the Marvel Comics universe This article has multiple issues. Please help improve it or discuss these issues on the talk page. (Learn how and when to remove these template messages) This article does not cite any sources. Please help improve this article by adding citations to reliable sources. Unsourced material may be challenged and removed.Find sources: The Jury comics – news · newspapers · books · scholar · JSTOR (June 2016…

Pour les articles homonymes, voir Gérard de Lorraine. Gérard de LorraineTitres de noblesseDuc de Lorraine1048-1070Prédécesseur Adalbert de LorraineSuccesseur Thierry II de LorraineComte de Metz1048-1070Prédécesseur Adalbert de LorraineSeigneur de Châtenois (d)jusqu'en 1070BiographieNaissance 1030Lieu inconnuDécès 14 avril 1070RemiremontSépulture RemiremontActivité FeudataireFamille Maison de LorrainePère Gerard de BouzonvilleMère Gisela (d)Fratrie Adalbert de LorraineConjoint H…

American politician John Joseph O'Neill, 1892 portrait John Joseph O'Neill (June 25, 1846 – February 19, 1898) was a U.S. Representative from Missouri. Born in St. Louis, Missouri, O'Neill attended the common schools. He studied law. He was admitted to the bar in 1870 and commenced practice in St. Louis. He engaged in the manufacture of gold pens. He served as member of the State house of representatives from 1872 to 1878. He served as member of the municipal assembly from 1879 to 1881. O'Neil…

This article needs additional citations for verification. Please help improve this article by adding citations to reliable sources. Unsourced material may be challenged and removed.Find sources: WROK AM – news · newspapers · books · scholar · JSTOR (April 2011) (Learn how and when to remove this template message) For the Sebastian, Florida, radio station, see WROK-FM. Radio station in Rockford, IllinoisWROKRockford, IllinoisBroadcast areaNorth Centra…

Mercedes-Benz C257InformasiProdusenDaimler AGMasa produksiMaret 2018 – sekarangPerakitanJerman: SindelfingenThailand: Samut Prakarn (Thonburi Automotive Assembly Plant)PerancangGorden WagenerBodi & rangkaKelasMobil eksekutif (E)Bentuk kerangka4-pintu sedanTata letakMesin depan, Penggerak roda belakang/Penggerak seluruh roda (4matic)PlatformMRAMobil terkaitMercedes-Benz W213Mercedes-Benz S-Class W222 faceliftMercedes-AMG GT 4-pintu CoupéMercedes-Benz C217[1]Penyalur dayaMesin1…

I WishPoster filmSutradaraHirokazu Kore-edaProduserKentarō KoikeHijiri TaguchiDitulis olehHirokazu Kore-edaPenata musikKishida ShigeruSinematograferYutaka YamasakiPenyuntingHirokazu Kore-edaPerusahaanproduksiShirogumi Inc.BIGXDistributorGagaTanggal rilis 11 Juni 2011 (2011-06-11) (Jepang) Durasi127 menitNegaraJepangBahasaJepangPendapatankotor$1,543,385[1] I Wish (奇跡code: ja is deprecated , Kiseki, terj. har.Miracle) adalah film Jepang tahun 2011 yang disunting, dituli…

يفتقر محتوى هذه المقالة إلى الاستشهاد بمصادر. فضلاً، ساهم في تطوير هذه المقالة من خلال إضافة مصادر موثوق بها. أي معلومات غير موثقة يمكن التشكيك بها وإزالتها. (يناير 2021) صدرت أربعة قرارات من مجلس الأمن التابع للأمم المتحدة خلال نزاع ناغورني كاراباخ. ولم تستشهد هذه القرارات بال…

Синелобый амазон Научная классификация Домен:ЭукариотыЦарство:ЖивотныеПодцарство:ЭуметазоиБез ранга:Двусторонне-симметричныеБез ранга:ВторичноротыеТип:ХордовыеПодтип:ПозвоночныеИнфратип:ЧелюстноротыеНадкласс:ЧетвероногиеКлада:АмниотыКлада:ЗавропсидыКласс:Птиц�…

Cet article est une ébauche concernant une commune du Calvados. Vous pouvez partager vos connaissances en l’améliorant (comment ?). Le bandeau {{ébauche}} peut être enlevé et l’article évalué comme étant au stade « Bon début » quand il comporte assez de renseignements encyclopédiques concernant la commune. Si vous avez un doute, l’atelier de lecture du projet Communes de France est à votre disposition pour vous aider. Consultez également la page d’aide à la …

Tullio d'Albisola, pseudonimo di Tullio Mazzotti (Albisola Superiore, 2 dicembre 1899 – Albissola Marina, 19 maggio 1971), è stato un ceramista, scultore, editore e scrittore italiano. Tullio d'Albisola e Lucio Fontana (!949) Indice 1 Biografia 1.1 Tullio futurista 1.2 La casa-laboratorio 1.3 Con l'editoria futurista 1.4 Lito-Latta 1.5 Scultura e ceramiche monumentali 1.6 Ultimi anni 2 Bibliografia 3 Voci correlate 4 Altri progetti 5 Collegamenti esterni Biografia Tullio Mazzotti era il secon…

イスラームにおける結婚(イスラームにおけるけっこん)とは、二者の間で行われる法的な契約である。新郎新婦は自身の自由な意思で結婚に同意する。口頭または紙面での規則に従った拘束的な契約は、イスラームの結婚で不可欠だと考えられており、新郎と新婦の権利と責任の概要を示している[1]。イスラームにおける離婚は様々な形をとることができ、個人的…

Motor vehicle Hyundai Custo (KU)OverviewManufacturerHyundaiAlso calledHyundai CustinProduction2021–presentAssemblyChina: Beijing (Beijing Hyundai)Taiwan: Hukou (Sanyang Motor)Vietnam: Ninh Bình (HTMV)Body and chassisClassMinivanBody style5-door minivanLayoutFront-engine, front-wheel-drivePlatformHyundai-Kia N3 platformRelatedKia Carnival (KA4)PowertrainEnginePetrol:1.5 L Smartstream G1.5 T-GDi I42.0 L Smartstream G2.0 T-GDi I4Transmission8-speed automaticDimensionsWheelbas…

Former administrative unit in Bangladesh Ancient ruins of Bikrampur Bikrampur (City of Courage) was a pargana situated 19 kilometres (12 mi) south of Dhaka, the modern capital city of Bangladesh. In the present day, it is known as the Munshiganj District of Bangladesh. It is a historic region in Bengal and was a part of the Bhawal Estate.[citation needed] History Part of a series on the History of Bangladesh Etymology Timeline Traditional Urheimat Ancient Neolithic, c. 7600 – c. 3…

Artikel ini memiliki beberapa masalah. Tolong bantu memperbaikinya atau diskusikan masalah-masalah ini di halaman pembicaraannya. (Pelajari bagaimana dan kapan saat yang tepat untuk menghapus templat pesan ini) Artikel atau bagian mungkin perlu ditulis ulang agar sesuai dengan standar kualitas Wikipedia. Anda dapat membantu memperbaikinya. Halaman pembicaraan dari artikel ini mungkin berisi beberapa saran. Artikel ini membutuhkan rujukan tambahan agar kualitasnya dapat dipastikan. Mohon bantu ka…

Island in the United States of America class=notpageimage| Location in Alaska King Island (Inupiaq: Ugiuvak; Russian: Остров Кинг, romanized: Ostrov King) (King's Island in early US sources) is an island in the Bering Sea, west of Alaska. It is about 40 miles (64 km) west of Cape Douglas and is south of Wales, Alaska. Geography King Island, Alaska. The large boulders on the top of the island are barely visible through the fog. King island is a small island located about 40 mi…

この項目には、一部のコンピュータや閲覧ソフトで表示できない文字が含まれています(詳細)。 数字の大字(だいじ)は、漢数字の一種。通常用いる単純な字形の漢数字(小字)の代わりに同じ音の別の漢字を用いるものである。 概要 壱万円日本銀行券(「壱」が大字) 弐千円日本銀行券(「弐」が大字) 漢数字には「一」「二」「三」と続く小字と、「壱」「弐」…

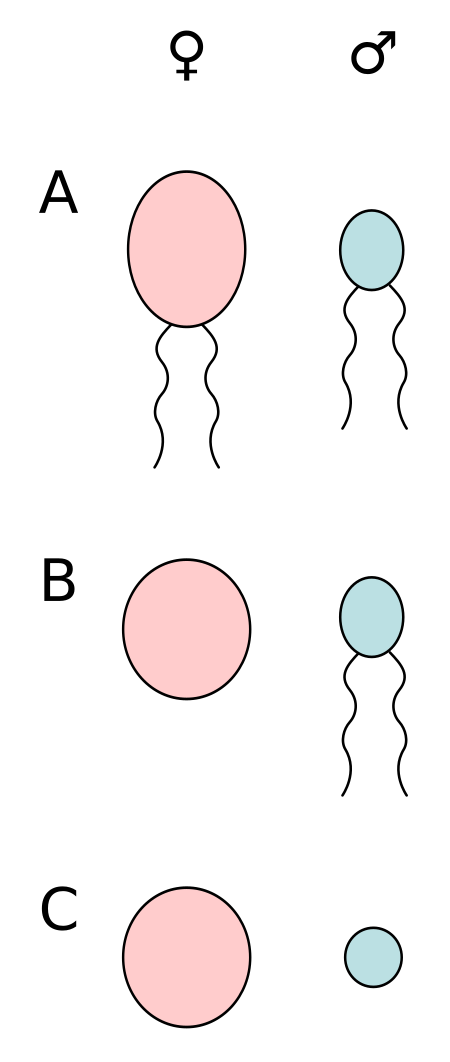

Beberapa bentuk anisogami. Anisogami (Anisogamy) adalah keadaan yang melibatkan peleburan gamet-gamet yang berlainan ukuran dan/atau motilitasnya. Pada oogami (oogamy), gamet-gamet berbeda dalam kedua sifat tersebut. Tampaknya sperma sering menyumbangkan sentriol tunggal untuk zigot yang terbentuk. Lihat pula Pembuahan atau fertilisasi Isogami Parthenogenesis Artikel bertopik biologi ini adalah sebuah rintisan. Anda dapat membantu Wikipedia dengan mengembangkannya.lbs

费迪南德·马科斯Ferdinand Marcos 菲律賓第10任總統任期1965年12月30日—1986年2月25日副总统費爾南多·洛佩斯(1965-1972)阿圖羅·托倫蒂諾前任奧斯達多·馬卡帕加爾继任柯拉蓉·阿基诺 菲律賓第4任總理任期1978年6月12日—1981年6月30日前任佩德羅·帕特諾(1899年)继任塞薩爾·維拉塔 个人资料出生1917年9月11日 美屬菲律賓北伊羅戈省薩拉特(英语:Sarrat)逝世1989年9月28日(1989…

Ivo Karlović Ivo Karlović durante lo US Open 2016 Nazionalità Croazia Altezza 211 cm Peso 104 kg Tennis Termine carriera 21 febbraio 2024 (ufficiale)[1] 4 ottobre 2021 (ultimo match) Carriera Singolare1 Vittorie/sconfitte 371-346 (52,70%) Titoli vinti 8 Miglior ranking 14º (18 agosto 2008) Risultati nei tornei del Grande Slam Australian Open 4T (2010) Roland Garros 3T (2014, 2016) Wimbledon QF (2009) US Open 4T (2016) Altri tornei Giochi olimpici 3…