VMEbus

|

This list of highest military decorations is an index to articles that describe the highest military decoration awarded by each country in the world. Note that some countries do not have separate civilian and military awards systems, and as such some countries' highest military awards may also be civilian awards. This list is incomplete; you can help by adding missing items. (March 2023) Country Image Name Date first awarded Number awarded Notes Argentina Cross to the Heroic Valour in Combat 18 …

artikel ini perlu dirapikan agar memenuhi standar Wikipedia. Masalah khususnya adalah: pada bagian sejarah untuk diupdate hingga tahun ini. Bagian prestasi dan seterusnya perlu dirapikan. Silakan kembangkan artikel ini semampu Anda. Merapikan artikel dapat dilakukan dengan wikifikasi atau membagi artikel ke paragraf-paragraf. Jika sudah dirapikan, silakan hapus templat ini. (Pelajari cara dan kapan saatnya untuk menghapus pesan templat ini) Penyuntingan Artikel oleh pengguna baru atau anonim unt…

George Best Informasi pribadiNama lengkap George BestTanggal lahir (1946-05-22)22 Mei 1946Tempat lahir Belfast, Irlandia UtaraTanggal meninggal 25 November 2005(2005-11-25) (umur 59)Tempat meninggal London, InggrisPosisi bermain WingerAttacking midfielderKarier junior1961–1963 Manchester UnitedKarier senior*Tahun Tim Tampil (Gol) 1963–1974 1974 1975 1975–1976 1976 1976–1977 1977–19781978–1979 1979–1980 1980–1981 1983 1983 1984 Manchester United→ Dunstable Town (pinjam) Sto…

Lambang Program Apollo. Dua belas orang pernah berjalan di Bulan, dimulai dari Neil Armstrong sebagai yang pertama hingga Gene Cernan sebagai orang yang terakhir. Semua pendaratan berawal di bulan terjadi antara Juli 1969 dan Desember 1972 sebagai bagian dari Program Apollo oleh NASA. Semua dua belas orang yang telah berjalan di Bulan merupakan pria berkebangsaan Amerika Serikat. Peta asal Lua error in package.lua at line 80: module 'Module:Location map/data/Amerika Serikat' not found. Daftar Fo…

PT Indosat TbkKantor pusat Indosat Ooredoo Hutchison di Jakarta(gedung hitam di tengah)Nama dagangIndosat Ooredoo HutchisonSebelumnya PT Indonesian Satellite Corporation (1967-1984) PT Indosat (Persero) Tbk (1984-2003) JenisPerseroan terbatas terbukaKode emitenIDX: ISATNYSE: IIT (1994–2013)IndustriTelekomunikasiPendahuluBimagraha Telekomindo (1992-2003)Satelindo (1993-2003)Indosat-M3 (2001-2003)Hutchison 3 Indonesia (2000-2022)Didirikan10 November 1967[1]PendiriITT CorporationKant…

Berikut ini adalah sebuah daftar gubernur Rajasthan.[1][2][3] Gubernur Rajasthan # Nama Mulai Menjabat Akhir Jabatan 1 Maharaj Man Singh II (Rajpramukh)[1][4] 30 Maret 1949 31 Oktober 1956 2 Gurumukh Nihal Singh 1 November 1956 16 April 1962 3 Sampurnanand 16 April 1962 16 April 1967 4 Sardar Hukam Singh 16 April 1967 1 Juli 1972 5 Sardar Jogendra Singh 1 Juli 1972 15 Februari 1977 6 Vedpal Tyagi (pelaksana jabatan) 15 Februari 1977 11 Mei 1977 7 Raghukul …

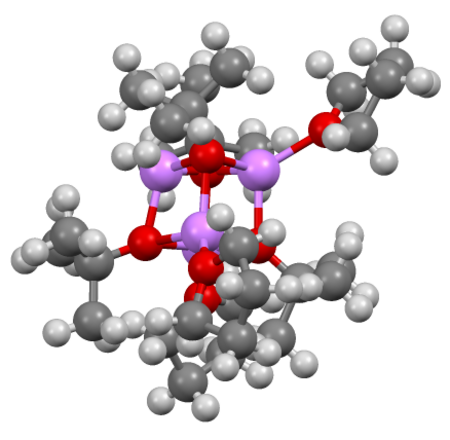

Struktur anion metoksida. Meskipun alkoksida logam alkali bukan termasuk garam dan memiliki struktur yang kompleks, secara kimiawi, mereka bertindak sebagai sumber RO−. Alkoksida adalah sebuah basa konjugat dari suatu alkohol sehingga mengandung gugus organik yang terikat pada atom oksigen yang bermuatan negatif. Alkoksida ditulis sebagai RO−, dengan R adalah substituen organik. Alkoksida adalah basa kuat dan, jika R tidak besar, merupakan nukleofil yang baik serta ligan yang bagus. Meskipun…

Saint Vincent and the GrenadinesPersonnelCaptainSunil AmbrisCoachNixon McleanTeam informationColoursYellow, Blue, GreenFounded1946Home groundArnos Vale StadiumHistoryFour Day winsn/aWICB Cup wins0Twenty20 wins0Official website[1] The Saint Vincent and the Grenadines national cricket team is a cricket team representing Saint Vincent and the Grenadines and is a member of the Windward Islands Cricket Board of Control. For cricketing purposes, players from Saint Vincent and the Grenad…

West Virginia election See also: 2020 United States secretary of state elections 2020 West Virginia Secretary of State election ← 2016 November 3, 2020 2024 → Nominee Mac Warner Natalie Tennant Party Republican Democratic Popular vote 447,537 320,650 Percentage 58.26% 41.74% Warner: 50–60% 60–70% 70–80% 80–90% Tennant: …

Artikel ini tidak memiliki referensi atau sumber tepercaya sehingga isinya tidak bisa dipastikan. Tolong bantu perbaiki artikel ini dengan menambahkan referensi yang layak. Tulisan tanpa sumber dapat dipertanyakan dan dihapus sewaktu-waktu.Cari sumber: .my – berita · surat kabar · buku · cendekiawan · JSTOR .myDiperkenalkan8 Juni 1987Jenis TLDRanah teratas kode negaraStatusAktifRegistriMalaysia Network Information Centre (MYNIC Berhad)SponsorMalaysia Netw…

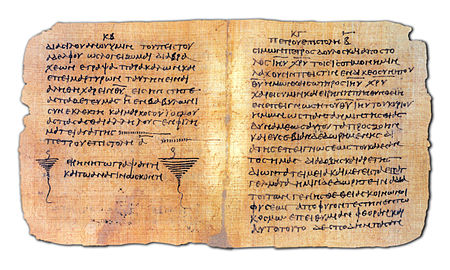

Bagian dari Alkitab KristenPerjanjian BaruLukas 7:36-37 pada Papirus 3 Injil Matius Markus Lukas Yohanes SejarahKisah Para Rasul Surat Surat-surat Paulus Roma 1 Korintus 2 Korintus Galatia Efesus Filipi Kolose 1 Tesalonika 2 Tesalonika 1 Timotius 2 Timotius Titus Filemon Ibrani Surat-surat umum Yakobus 1 Petrus 2 Petrus 1 Yohanes 2 Yohanes 3 Yohanes Yudas ApokalipsWahyu Perjanjian Lama Portal Kristenlbs Bagian dari serial tentangSanto Petrus Dalam Perjanjian Baru Berjalan di atas air Pe…

Artikel ini sebatang kara, artinya tidak ada artikel lain yang memiliki pranala balik ke halaman ini.Bantulah menambah pranala ke artikel ini dari artikel yang berhubungan atau coba peralatan pencari pranala.Tag ini diberikan pada Desember 2022. Untuk musikologis AS, lihat Robert Walser (musikologis). Robert Otto WalserRobert Walser pada sekitar tahun 1900Lahir(1878-04-15)15 April 1878Biel/Bienne, SwissMeninggal25 Desember 1956(1956-12-25) (umur 78)dekat Herisau, SwissPekerjaanPenulisKebang…

artikel ini perlu dirapikan agar memenuhi standar Wikipedia. Tidak ada alasan yang diberikan. Silakan kembangkan artikel ini semampu Anda. Merapikan artikel dapat dilakukan dengan wikifikasi atau membagi artikel ke paragraf-paragraf. Jika sudah dirapikan, silakan hapus templat ini. (Pelajari cara dan kapan saatnya untuk menghapus pesan templat ini) Ada usul agar Bangsa Moro diganti judulnya dan dipindahkan ke Orang Moro (Diskusikan). Artikel ini bukan mengenai Moor ataupun suku Moor. Suku Mo…

Chronologie de la France ◄◄ 1585 1586 1587 1588 1589 1590 1591 1592 1593 ►► Chronologies 1er août : Jacques Clément assassine le roi à coup de couteau.Données clés 1586 1587 1588 1589 1590 1591 1592Décennies :1550 1560 1570 1580 1590 1600 1610Siècles :XIVe XVe XVIe XVIIe XVIIIeMillénaires :-Ier Ier IIe IIIe Chronologies thématiques Art Architecture, Arts plastiques (Dessin, Gravure, Peinture et Sculpture), …

2013 concert tour by Rihanna Diamonds tour redirects here. Not to be confused with Diamond Tour. For the concert tour by Julie Bergan, see Diamonds Tour (Julie Bergan). Diamonds World TourTour by RihannaPromotional poster for the tourAssociated albumUnapologeticStart dateMarch 8, 2013 (2013-03-08)End dateNovember 15, 2013 (2013-11-15)Legs5No. of shows96Box office$140.1 million ($183.25 in 2023 dollars)[1]Rihanna concert chronology Loud Tour(2011) Diamonds Wo…

Symbol used in drawings Diagram showing the rod and vane inserted into the soil US Army Corps of Engineers personnel carrying out a shear vane test The shear vane test is a method of measuring the undrained shear strength of a cohesive soil. The test is carried out with equipment consisting of a rod with vanes mounted to it that is inserted into the ground and rotated. A gauge on the top of the rod measures the torque required to cause failure of the soil and provides a conversion to shear stren…

Shinkansen seri E8Rangkaian G1 menjalani uji coba pada Februari 2023Beroperasi2024 (rencana)JenisMini-shinkansenDigantikan olehShinkansen E3Tahun pembuatan2022–2026 (rencana)Jumlah sudah diproduksi7 kereta (1 rangkaian)Formasi7 keretaKapasitas355 (26 kelas Hijau + 329 kelas Standar)OperatorJR EastJalurTohoku Shinkansen, Yamagata ShinkansenData teknisPintu1 per sisiKecepatan maksimum300 km/h (186 mph) (Tohoku Shinkansen), 130 km/h (81 mph) (Yamagata Shinkansen)Sistem listrik…

Sampul buku A Mathematician's Apology adalah esai yang ditulis pada tahun 1940 oleh matematikawan Britania G. H. Hardy. Esai ini membahas estetika matematika dan isi pribadi, dan memberikan wawasan kepada orang awam tentang pikiran seorang matematikawan aktif. Ringkasan isi Pada judul buku ini, Hardy menggunakan kata apology (apologia atau pembelaan) dalam arti pembenaran formal atau pembelaan (seperti dalam karya Plato Apologia Sokrates), bukan dalam arti meminta maaf. Hardy merasa perlu untuk …

1939–1940 Soviet puppet state in occupied Karelia Finnish Democratic RepublicSuomen kansanvaltainen tasavalta Demokratiska Republiken Finland1939–1940 Seal[1] Anticipated territorial changes of the Finnish Democratic Republic, with areas to be ceded to the Soviet Union (red) and to the Finnish Democratic Republic (green).StatusPuppet state of the Soviet UnionCapitalHelsinki (de jure)Terijoki (de facto)GovernmentOne-party socialist republic under a Stalinist totalitarian dictatorshipC…

1958 song composed by Ross Bagdasarian Sr. performed by Alvin and the Chipmunks This article needs additional citations for verification. Please help improve this article by adding citations to reliable sources. Unsourced material may be challenged and removed.Find sources: The Chipmunk Song Christmas Don't Be Late – news · newspapers · books · scholar · JSTOR (June 2016) (Learn how and when to remove this template message) The Chipmunk Song (Christm…